## DIGITAL ELECTRONICS SYSTEM DESIGN

**FALL 2019**

**PROF. IRIS BAHAR**

**SEPTEMBER 25, 2019**

**LECTURE 7: CMOS TRANSISTORS**

## STORAGE SPACE IN LAB

- Unfortunately, there is no secure storage space available in B&H 196

- However, we do have open shelves and drawers in the back end of the room

- You are free to leave your kits there, but it is at your own risk

- Put all parts in an enclosed bin (e.g., Tupperware with lid)

- Write your name clearly on bin

- Do no leave valuables in the bin

## **CLARIFICATION ABOUT DEADLINES**

- Labs are due in groups:

- Group I: labs 0-3 due by Sunday, October 6

- Group 2: labs 4-9 due by Sunday, November 17

- Group 3: labs A and B due by Friday, December 6

- The last week before the final exam can be used as a grace period:

- Up to one additional lab from each group can be checked off between Dec. 7-13

- Labs may be checked off earlier, but if completed after the group deadline, they will

count as being checked off during exam week

- Only one lab a day credited in exam week

- Labs C and D may be checked off up until Thursday, Dec. 13

- Plan ahead! Don't wait until exam week to finish all your labs!

## IBM STUDENT DESIGN WORKSHOP

WHEN: October 12, 2019

TIME: 9:00am-5:00pm

Open to all students, but geared mostly toward engineering students in their junior year.

IBM facilitators will guide students through design for tackling a current pressing problem (e.g., within the or for a course)

- Advanced registration is required. Please reserve your spot by Friday, Sept. 27 at https://forms.gle/ynUg4rixslbTy8Qi6

- Some intial problem evaluation is required before the workshop takes place

## WHAT IS DESIGN THINKING?

- Design thinking is a methodology for creative problem solving that enables collaboration across disciplines.

- It can be applied to many different kinds of problems

- It can help many different people (including engineers) think about problem solving in new ways

## STUDENT WORKSHOP BRIEF

- Learn how to use an enhanced form of design thinking to creatively solve problems collaboratively with fellow students.

- We'll tackle a real-world problem, and bring potential solutions from problem discovery through to prototyping using an agile and user-centered approach.

- Join us and learn a set of methods that you can use to solve almost any kind of design challenge.

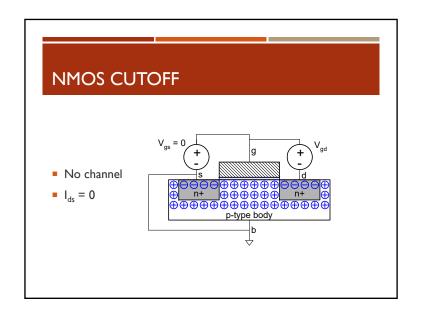

# NMOS TRANSISTOR $g = 0: \text{ gate is at low voltage } (V_{gs} < V_{thn}) \text{ g} = 0 \qquad g = 1$ p - type body is at low voltage transistor is OFF (no current flows) $g = 1: \text{ gate is at a high voltage } (V_{gs} \ge V_{thn}) \text{ source } Gate \text{ Drain Polysilicon}$ negative charge attracted to body negative charge attracted to body newerts a channel under gate to n-type transistor is ON (current flows) transistor acts as resistor

## **CROSSING THE CHANNEL**

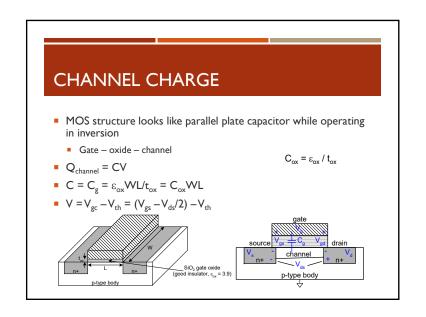

- Now we know

- How much charge Q<sub>channel</sub> is in the channel

- How much time, t, does it take to cross channel?

- $t = \frac{L}{v} = \frac{L}{\mu E}$ , where  $\mu$  is mobility, E is electric field across the channel, or  $E = V_{ds}/L$

- So now,  $t = \frac{L}{\mu \frac{V_{ds}}{t}} = \frac{L^2}{\mu V_{ds}}$

- Typical values for mobility:

- for NFETs:  $\mu_n = 1400 \text{ cm}^2/\text{V-sec}$

- for PFETs:  $\mu_p = 450 \text{ cm}^2/\text{V-sec}$

- More of a function of doping than technology node size

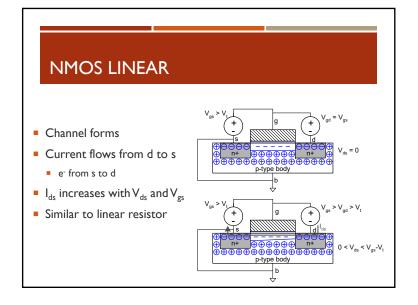

### **NMOS LINEAR I-V**

- Now we know

- How much charge Q<sub>channel</sub> is in the channel

- How much time, t, each carrier takes to cross channel

$$I_{ds} = \frac{Q_{channel}}{t}$$

$$= \mu C_{ox} \frac{W}{L} (V_{gs} - V_{th} - V_{ds}/2) V_{ds}$$

$$= \beta (V_{gs} - V_{th} - V_{ds}/2) V_{ds} \qquad \beta = \mu C_{ox} \frac{W}{L}$$

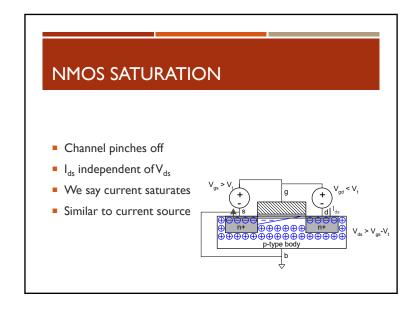

## NMOS SATURATION I-V

- When  $V_{ds} > V_{dsat}$ , where  $V_{dsat} = V_{gs} Vt$

- channel is no longer inverted around the drain;

- channel pinches off near drain

- Increasing V<sub>ds</sub> has no further effect on current

$$I_{ds} = \beta (V_{gs} - V_{th} - V_{ds}/2) V_{ds}$$

=  $\frac{\beta}{2} (V_{gs} - V_{th})^2$

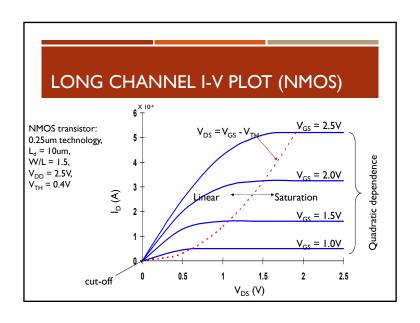

## **NMOS I-V SUMMARY**

Shockley Ist order transistor models

$$I_{ds} = \begin{cases} 0 & V_{gs} < V_{th} & \text{cutoff} \\ \beta \left( V_{gs} - V_{th} - \frac{V_{ds}}{2} \right) V_{ds} & V_{ds} < V_{dsat} & \text{linear} \\ \frac{\beta}{2} \left( V_{gs} - V_{th} \right)^2 & V_{ds} > V_{dsat} & \text{saturation} \end{cases}$$

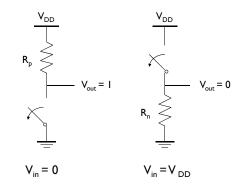

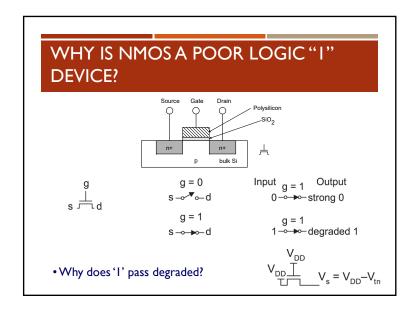

# CMOS INVERTER: STEADY STATE RESPONSE