### DIGITAL ELECTRONICS SYSTEM DESIGN

**FALL 2019**

**PROF. IRIS BAHAR**

**SEPTEMBER 30, 2019**

LECTURE 8: CMOS GATES & INTRODUCTION TO VERILOG

#### IBM STUDENT DESIGN WORKSHOP

WHEN: October 12, 2019

TIME: 9:00am-5:00pm

- Open to all students, but geared mostly toward engineering students in their junior year.

- IBM facilitators will guide students through design for tackling a current pressing problem (e.g., within the or for a course)

- Advanced registration is required. Please reserve your spot by Thursday, Oct. 3 at https://forms.gle/ynUg4rixslbTy8Qi6

- Email Elizabeth Austin or Jennifer Casasanto for additional questions.

#### **CLARIFICATION ABOUT DEADLINES**

- Labs are due in groups:

- Group I: labs 0-3 due by Sunday, Oct. 6 (lab I & 2 both required)

- Group 2: labs 4-9 due by Sunday, Nov. 17 (lab 9, and either 7 or 8 required)

- Group 3: labs A and B due by Friday, Dec. 6

- Group 4: labs C and D due by Thursday, Dec. 13 (one of lab B, C, D required)

- The last week before the final exam can be used as a grace period:

- Up to one additional lab from group 1-3 can be checked off between Dec. 7-13

- Labs may be checked off earlier, but if completed after the group deadline, they will

count as being checked off during exam week

- Only one lab a day credited in exam week

- Plan ahead! Don't wait until exam week to finish all your labs!

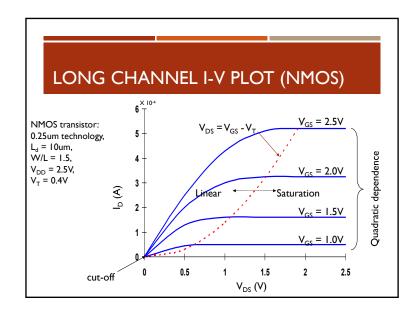

#### **NMOS I-V SUMMARY**

Shockley Ist order transistor models

$$I_{ds} = \begin{cases} 0 & V_{gs} < V_{th} & \text{cutoff} \\ \beta \left(V_{gs} - V_{th} - \frac{V_{ds}}{2}\right) V_{ds} & V_{ds} < V_{dsat} & \text{linear} \\ \frac{\beta}{2} \left(V_{gs} - V_{th}\right)^2 & V_{ds} > V_{dsat} & \text{saturation} \end{cases}$$

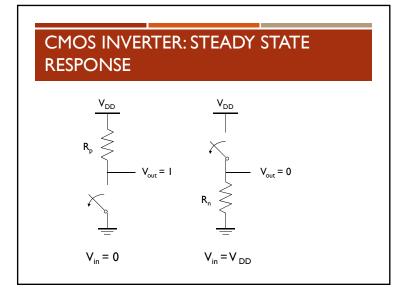

- Full rail-to-rail swing → high noise margins

- Logic levels independent of device sizes → ratioless

- Always a path to V<sub>dd</sub> or GND in steady state → less sensitive to noise

- nearly zero steady-state input current

- No direct path steady-state between power and ground

- no static power dissipation

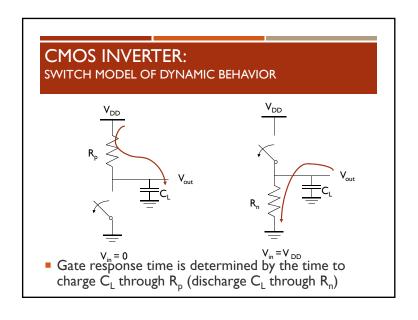

- Propagation delay is a function of load capacitance and resistance of transistors

### CMOS INVERTER: DYNAMIC BEHAVIOR

Transient, or dynamic, response determines the maximum speed at which a device can be operated.

$$t_{pHL} = f(R_n, C_L)$$

#### **CONSTRUCTION OF PDN**

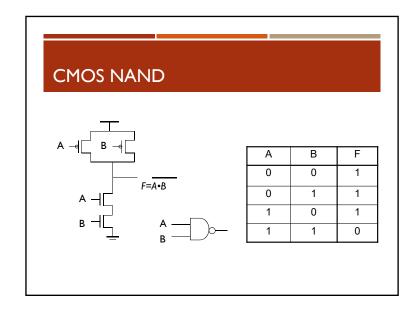

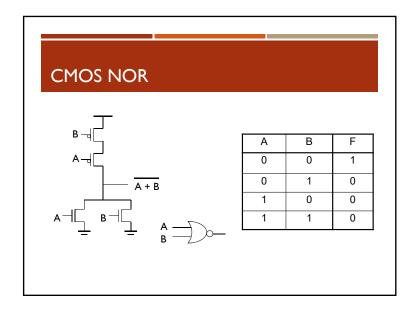

NMOS devices in series implement a NAND function

NMOS devices in parallel implement a NOR function

$$A \rightarrow \begin{bmatrix} & & & \\ & & & \\ & & & \end{bmatrix} \xrightarrow{A + B}$$

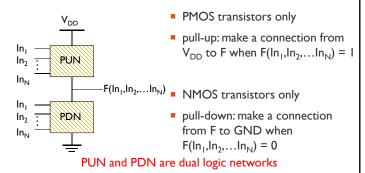

#### STATIC COMPLEMENTARY CMOS

Pull-up network (PUM) and pull-down network (PDN)

### **DUAL PUN AND PDN**

- PUN and PDN are dual networks

- DeMorgan's theorems

- $\overline{A + B} = \overline{A \cdot B}$  [!(A + B) = !A !B or !(A | B) = !A & !B]

- $\overline{A \cdot B} = \overline{A} + \overline{B}$  [!(A \cdot B) = !A + !B or !(A \cdot B) = !A | !B]

- a parallel connection of transistors in the PUN corresponds to a series connection of the PDN

- Complementary gate is naturally inverting (NAND, NOR, AOI, OAI)

- Number of transistors for an N-input logic gate is 2N

## PULL UP RESISTORS AND TRISTATE DRIVERS

- Lab 2 discusses use of pull-up resistors and tristate drivers

- Why use them?

INTRODUCTION TO THE VERILOG HARDWARE DESCRIPTION LANGUAGE

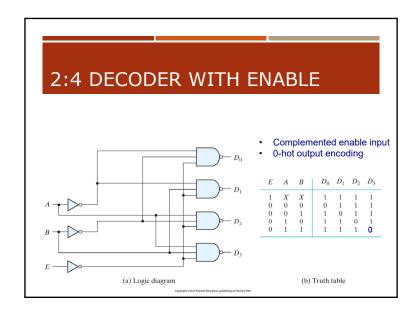

#### 2:4 DECODER: STRUCTURAL // Gate-level (structural) description of 2-to-4 decoder module decoder 2x4 gates(D, A, B, enable); output [3:0] D; input A, B, enable\_; wire A not, B not, enable not; multi-bit output not G1(A not, A); not G2(B not, B); not G3 (enable not, enable ); nand G4(D[0], A not, B not, enable not); nand G5(D[1], A\_not, B, enable\_not); nand G6(D[2], A, B not, enable not); nand G7(D[3], A, B, enable not); endmodule

## 2:4 DECODER: BEHAVIORAL (DATAFLOW)

left hand side must be a wire (or output)

# 2:4 DECODER: BEHAVIORAL 2 (DATAFLOW)

```

// Behavioral description of 2-to-4 decoder

// inputs A and B replaced with I[1:0]

module decoder 2x4 beh2(D, I, enable);

[3:0] D;

output

[1:0] I;

input

input

enable ;

conditional continuous

wire

[3:0] Di;

assignment statement

assign Di = (I == 2'b11) ? 4'b0111:

(I == 2'b10) ? 4'b1011: <

(I == 2'b01) ? 4'b1101: 4'b1110;

assign D = (enable_ == 1'b0) ? Di : 4'b1111;

endmodule

```