#### DIGITAL ELECTRONICS SYSTEM DESIGN

FALL 2019

PROFS. IRIS BAHAR & ROD BERESFORD OCTOBER 23, 2019 LECTURE 14: STATE MACHINE DESIGN

# VERILOG TUTORIAL (PART 2)

- McKenna will again give a Verilog tutorial during his lab hours this Wednesday from 4:30-6:30

- He will go over state machine design with Verilog as well as procedures to set up a simulation with Verilog

#### MIDTERM STUDY SESSION

- Jiwon will give a help session on Monday, Oct. 28 from 7-9pm in B&H190 to prepare for the midterm exam next week.

- Come with questions. She will also solve some problems (from the problem sets) on the board.

- Solutions to practice problem set #1 will be available later tonight

- She will hold office hours in B&H 196 this week and next:

- Saturday, Oct. 26 : 10am-noon

- Sunday, Oct. 27: 7-9pm

- Tuesday, Oct 29: 7-9pm

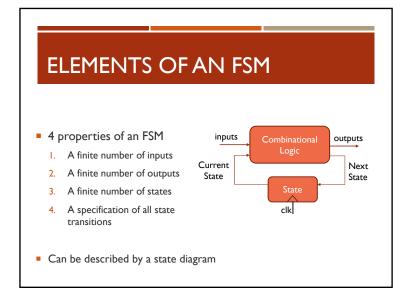

# FINITE STATE MACHINE $\begin{array}{c} \stackrel{inputs}{\underbrace{Current}\\ \underbrace{Logic}\\ \underbrace{Vertic}\\ \underbrace{State}\\ \underbrace{Sta$

current state and input values

# STATE MACHINE ANALYSIS PROCEDURE

- I. Given a circuit diagram for a sequential circuit

- 2. Derive expressions for FF inputs (or state equations for each FF)

- Derive an equation for each output as a function of the present state (and the inputs - Mealy only)

- 4. Set up a state table

- Present state, inputs, next state, output

- Optional intermediate columns for FF inputs

- 5. Draw the state diagram

# EXAMPLE OF SEQUENTIAL CIRCUIT Is this a Moore or Mealy machine? Is this a Moore or Mealy machine? Is this a Moore or Mealy machine?

# STATE TABLE FOR CIRCUIT

|                 |   | sent<br>ate | Input |   | ext<br>ate | Output |

|-----------------|---|-------------|-------|---|------------|--------|

| State equations | Α | В           | x     | A | B          | Y      |

|                 | 0 | 0           | 0     | 0 | 0          | 0      |

|                 | 0 | 0           | 1     | 0 | 1          | 0      |

|                 | 0 | 1           | 0     | 0 | 0          | 1      |

|                 | 0 | 1           | 1     | 1 | 1          | 0      |

|                 | 1 | 0           | 0     | 0 | 0          | 1      |

|                 | 1 | 0           | 1     | 1 | 0          | 0      |

| 9               | 1 | 1           | 0     | 0 | 0          | 1      |

|                 | 1 | 1           | 1     | 1 | 0          | 0      |

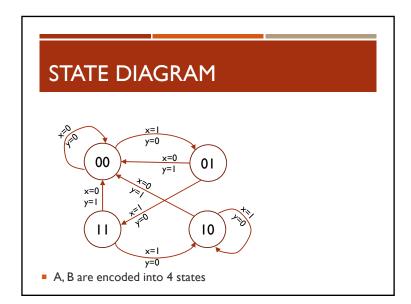

# ALTERNATIVE FORM FOR THE STATE TABLE

#### State diagram?

| Dro | sent | N          | lext | Stat       | e   | Output |              |

|-----|------|------------|------|------------|-----|--------|--------------|

|     | ate  | <i>x</i> = | 0    | <b>x</b> = | = 1 | x = 0  | <i>x</i> = 1 |

| Α   | В    | Α          | B    | Α          | B   | Y      | y            |

| 0   | 0    | 0          | 0    | 0          | 1   | 0      | 0            |

| 0   | 1    | 0          | 0    | 1          | 1   | 1      | 0            |

| 1   | 0    | 0          | 0    | 1          | 0   | 1      | 0            |

| 1   | 1    | 0          | 0    | 1          | 0   | 1      | 0            |

# EXAMPLE OF SEQUENTIAL CIRCUIT Image: style style

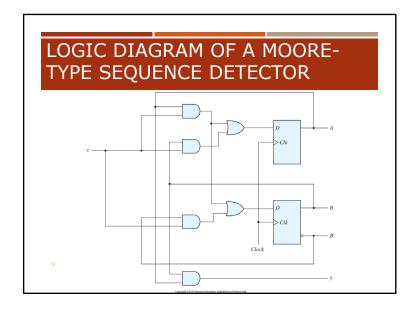

#### STATE MACHINE DESIGN PROCEDURE

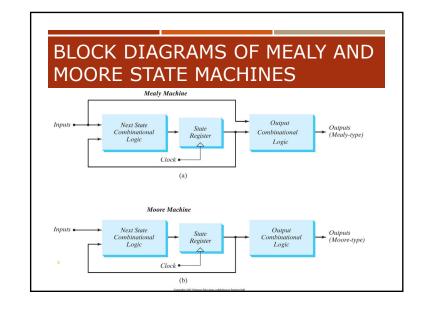

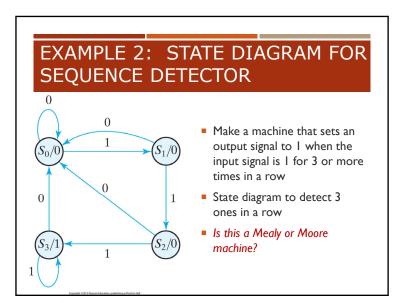

- I. Define the task in words (Mealy or Moore?)

- 2. Draw a state diagram

- 3. Assign state values to the states (number the states)

- 4. Minimize the number of states in the state table/diagram

- 5. Set up a state table

- 6. Select a flip-flop type and set up an excitation table

- 7. Use the excitation table to generate columns in the state table for the FF inputs

- 8. Design the combinational circuits

- 9. Draw the logic diagram and build the circuit

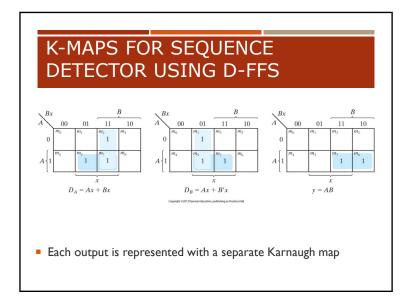

#### STATE TABLE FOR SEQUENCE DETECTOR: MOORE MACHINE

|   | sent<br>ate | Input<br>x | Next<br>State |   | Output |  |

|---|-------------|------------|---------------|---|--------|--|

| A | В           |            | Α             | В | y      |  |

| 0 | 0           | 0          | 0             | 0 | 0      |  |

| 0 | 0           | 1          | 0             | 1 | 0      |  |

| 0 | 1           | 0          | 0             | 0 | 0      |  |

| 0 | 1           | 1          | 1             | 0 | 0      |  |

| 1 | 0           | 0          | 0             | 0 | 0      |  |

| 1 | 0           | 1          | 1             | 1 | 0      |  |

| 1 | 1           | 0          | 0             | 0 | 1      |  |

| 1 | 1           | 1          | 1             | 1 | 1      |  |

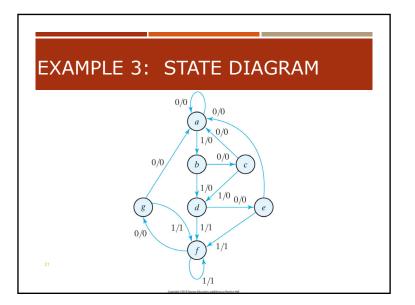

## STATE TABLE DERIVED FROM DIAGRAM

|               | Next  | State        | Output |              |  |

|---------------|-------|--------------|--------|--------------|--|

| Present State | x = 0 | <i>x</i> = 1 | x = 0  | <i>x</i> = 1 |  |

| а             | а     | b            | 0      | 0            |  |

| b             | С     | d            | 0      | 0            |  |

| С             | а     | d            | 0      | 0            |  |

| d             | е     | f            | 0      | 1            |  |

| e             | а     | f            | 0      | 1            |  |

| f             | g     | f            | 0      | 1            |  |

| < Z           | а     | f            | 0      | 1:>          |  |

| REDUCING 1        | THE S | STATE -                          | TABLE                        |              |

|-------------------|-------|----------------------------------|------------------------------|--------------|

|                   |       | now, d and f g<br>d have the san | to to the same<br>ne outputs | place        |

|                   | Next  | Out                              | Output                       |              |

| Present State     | x = 0 | <i>x</i> = 1                     | x = 0                        | <i>x</i> = 1 |

| а                 | а     | b                                | 0                            | 0            |

| b g is gone       | С     | d                                | 0                            | 0            |

| C Where g was _   | a     | d                                | 0                            | 0            |

| < d gets replaced | е     | f                                | 0                            | 12           |

| e by e            | а     | f                                | 0                            | 1            |

| <                 | е     | f                                | 0                            | 12           |

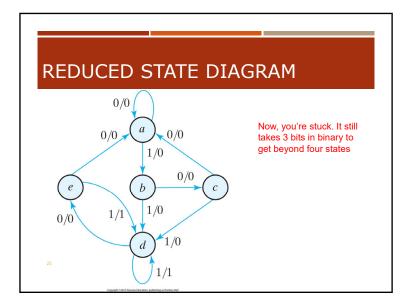

## REDUCED STATE TABLE

|         |                                             | Next State   |              | Output |              |

|---------|---------------------------------------------|--------------|--------------|--------|--------------|

| Present | State                                       | <i>x</i> = 0 | <i>x</i> = 1 | x = 0  | <i>x</i> = 1 |

| а       | So, wherever<br>f was, replace<br>it with d | а            | b            | 0      | 0            |

| b       |                                             | С            | d            | 0      | 0            |

| С       |                                             | а            | d            | 0      | 0            |

| d       |                                             | е            | d            | 0      | 1            |

| е       |                                             | а            | d            | 0      | 1            |

| ыаг    | E ASSIGN                | LE BINARY<br>MENTS         |                                              |

|--------|-------------------------|----------------------------|----------------------------------------------|

|        |                         |                            | a 1/0                                        |

| State  | Assignment 1,<br>Binary | Assignment 2,<br>Gray Code | Assignment 3,<br>One-Hot                     |

| а      | 000                     | 000                        | 00001                                        |

|        | 001                     | 001                        | 00010                                        |

| b      | 010                     | 011                        | 00100                                        |

| b<br>c | 010                     |                            |                                              |

| U      | 010                     | 010                        | 01000                                        |

| c      | 010                     | 010<br>110                 | $\begin{array}{c} 01000\\ 10000 \end{array}$ |

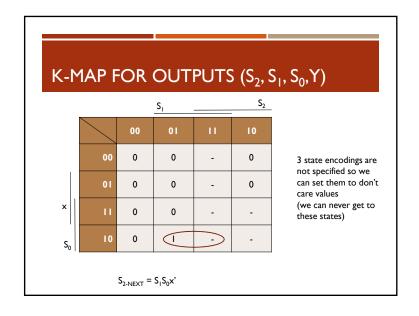

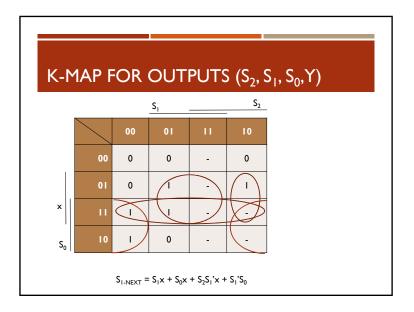

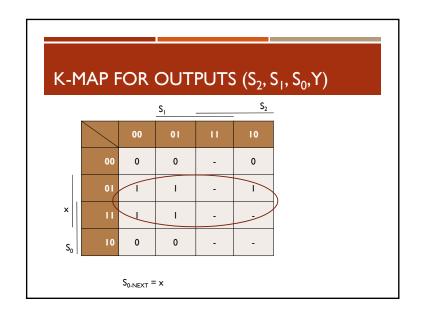

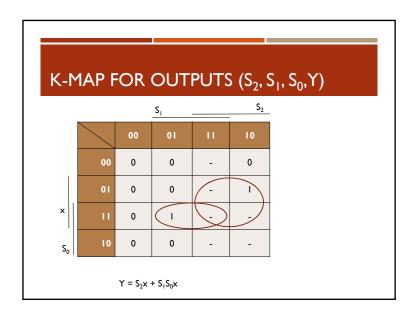

# REDUCED STATE TABLE WITH BINARY ASSIGNMENT 1

|               | Next  | State        | Output |              |

|---------------|-------|--------------|--------|--------------|

| Present State | x = 0 | <i>x</i> = 1 | x = 0  | <i>x</i> = 1 |

| 000           | 000   | 001          | 0      | 0            |

| 001           | 010   | 011          | 0      | 0            |

| 010           | 000   | 011          | 0      | 0            |

| 011           | 100   | 011          | 0      | 1            |

| 100           | 000   | 011          | 0      | 1            |

#### **VERILOG PROCEDURAL BLOCKS -REVIEW**

always @(A or B or C) begin Q = D; // Q must be of type reg . . . end

always @(posedge clock or negedge reset)

always @(posedge clock, negedge reset)

#### **FSM IN VERILOG**

Suggested coding style for FSMs

<module statement>

<input and output declarations> <reg declarations>

<parameter and typedef statement>

<always block for next state>

<always block for output>

<always block for state FFs>

endmodule

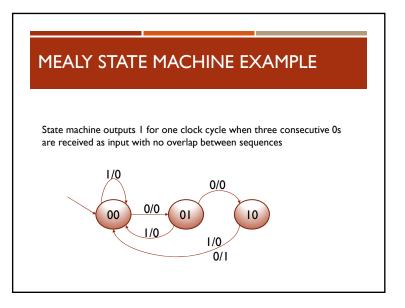

#### MEALY STATE MACHINE EXAMPLE module example state machine(clock, reset, in, out); output out; input clock, reset, in; reg [1:0] Scurr, Snext; parameter S0=2'b00, S1=2'b01, S2=2'b10; always @(in, reset, Scurr) begin if (reset == 1) Snext = S0; else case (Scurr) S0: if (in == 1) Snext = S0; else S1; S1: if (in == 1) Snext = S0; else S2; default: Snext = S0; endcase end always @(in, Scurr) if ((Scurr == S2) && (in == 0)) out = 1; else out = 0; always @(posedge clock)

#### MEALY STATE MACHINE EXAMPLE -**VERSION 2**

module example state machine(clock, reset, in, out); output out; input clock, reset, in; reg [1:0] Scurr, Snext; parameter S0=2'b00, S1=2'b01, S2=2'b10; always @(in, Scurr) begin case (Scurr) S0: if (in == 1) Snext = S0; else S1; S1: if (in == 1) Snext = S0; else S2; default: Snext = S0; endcase end always @(in, Scurr) if ((Scurr == S2) && (in == 0)) out = 1; else out = 0; always @(posedge clock) if (reset == 1) Scurr <= S0; <---assumes FF has reset input else Scurr <= Snext; endmodule

### MEALY STATE MACHINE EXAMPLE – TESTBECH

| <pre>module example_state_machine_testbench; wire out;</pre> |

|--------------------------------------------------------------|

| reg clock, reset, in;                                        |

| icg clock, lebec, in,                                        |

| example state machine M0(clock, reset, in, out)              |

| initial                                                      |

| begin                                                        |

| reset = 1'b0; // initialize inputs                           |

| clock = 1'b0;                                                |

| in = 1'b0;                                                   |

| #4 reset = 1'b1;                                             |

| #6 reset = 1'b0;                                             |

| #19 in = 1'b1;                                               |

| <pre>#100 \$finish; // end simulation</pre>                  |

| end                                                          |

| always                                                       |

| begin                                                        |

| <pre>#10 clock = ~clock;</pre>                               |

| end                                                          |

| endmodule                                                    |