## UPDATED LAB TA HOURS

- Pratishtha will be away attending a conference this week

- She is canceling her Tuesday hours from 10am-noon

- She will hold normal hours on Friday from I-4pm

### MIDTERM STUDY SESSION

- Jiwon will give a help session on Monday, Oct. 28 from 7-9pm in B&H190 to prepare for the midterm exam next week.

- Come with questions. She will also solve some problems (from the problem sets) on the board.

- She will hold office hours in B&H 196 this Tuesday, Oct. 29 from 7-9pm

- Practice Problem Set #2 has been posted (as well as solutions)

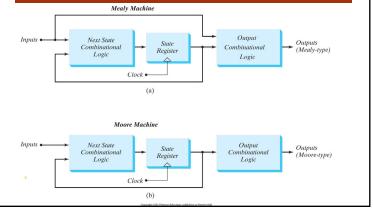

## BLOCK DIAGRAMS OF MEALY AND MOORE STATE MACHINES

#### STATE MACHINE DESIGN PROCEDURE

- I. Define the task in words (Mealy or Moore?)

- 2. Draw a state diagram

- 3. Assign state values to the states (number the states)

- 4. Minimize the number of states in the state table/diagram

- 5. Set up a state table

- 6. Select a flip-flop type and set up an excitation table

- 7. Use the excitation table to generate columns in the state table for the FF inputs

- 8. Design the combinational circuits

- 9. Draw the logic diagram and build the circuit

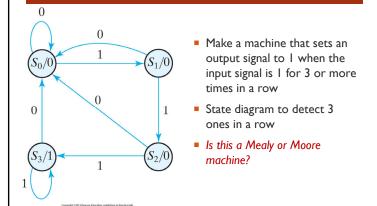

# EXAMPLE 2: STATE DIAGRAM FOR SEQUENCE DETECTOR

## STATE TABLE FOR SEQUENCE DETECTOR: MOORE MACHINE

|   | ate | Input | Next<br>State |   | Output |

|---|-----|-------|---------------|---|--------|

| Α | В   | x     | Α             | В | у      |

| 0 | 0   | 0     | 0             | 0 | 0      |

| 0 | 0   | 1     | 0             | 1 | 0      |

| 0 | 1   | 0     | 0             | 0 | 0      |

| 0 | 1   | 1     | 1             | 0 | 0      |

| 1 | 0   | 0     | 0             | 0 | 0      |

| 1 | 0   | 1     | 1             | 1 | 0      |

| 1 | 1   | 0     | 0             | 0 | 1      |

| 1 | 1   | 1     | 1             | 1 | 1      |

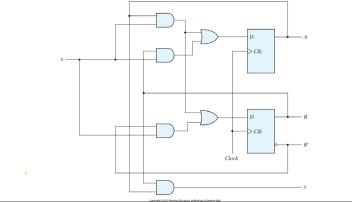

#### K-MAPS FOR SEQUENCE DETECTOR USING D-FFS 00 01 00 01 11 10 11 00 01 11 10 1 1 1 1 1 1 $D_A = Ax + Bx$ $D_B = Ax + B'x$ y = AB• Each output is represented with a separate Karnaugh map

# LOGIC DIAGRAM OF A MOORE-TYPE SEQUENCE DETECTOR

#### STATE TABLE DERIVED FROM DIAGRAM

|               | Next  | State        | Output |              |  |

|---------------|-------|--------------|--------|--------------|--|

| Present State | x = 0 | <i>x</i> = 1 | x = 0  | <i>x</i> = 1 |  |

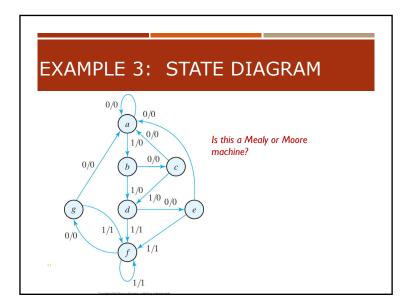

| а             | а     | b            | 0      | 0            |  |

| b             | С     | d            | 0      | 0            |  |

| С             | а     | d            | 0      | 0            |  |

| d             | е     | f            | 0      | 1            |  |

| e             | а     | f            | 0      | T            |  |

| f             | g     | f            | 0      | 1            |  |

| <.g           | а     | f            | 0      | 1:>          |  |

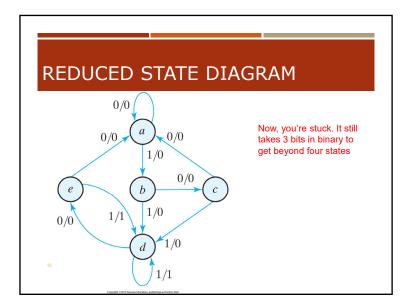

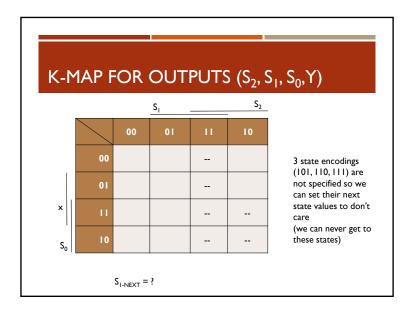

#### REDUCED STATE TABLE

|               | Next                              | State        | Output |              |  |

|---------------|-----------------------------------|--------------|--------|--------------|--|

| Present State | $\boldsymbol{x} = \boldsymbol{0}$ | <i>x</i> = 1 | x = 0  | <i>x</i> = 1 |  |

| 000           | 000                               | 001          | 0      | 0            |  |

| 001           | 010                               | 011          | 0      | 0            |  |

| 010           | 000                               | 011          | 0      | 0            |  |

| 011           | 100                               | 011          | 0      | 1            |  |

| 100           | 000                               | 011          | 0      | 1            |  |

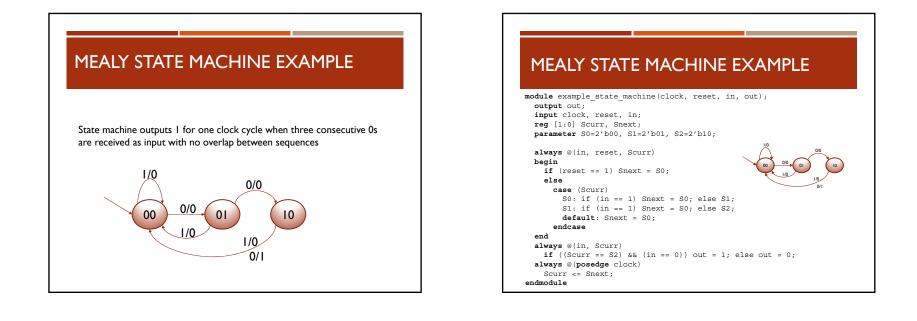

|                   | EALY STATE MACHINE EXAMPLE –<br>RSION 2                                                                                                                  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| out<br>ing<br>reg | <pre>e example_state_machine(clock, reset, in, out); put out; put clock, reset, in; [1:0] Scurr, Snext; ammeter S0=2'b00, S1=2'b01, S2=2'b10;</pre>      |

|                   | <pre>rays @(in, Scurr) regin case (Scurr) S0: if (in == 1) Snext = S0; else S1; S1: if (in == 1) Snext = S0; else S2; default: Snext = S0; endcase</pre> |

| alw               | nnd<br>γays @(in, Scurr)<br>.f ((Scurr == S2) && (in == 0)) out = 1; else out = 0;                                                                       |

| i                 | <pre>rays @(posedge clock) f (reset == 1) Scurr &lt;= S0;  assumes FF has reset input lse Scurr &lt;= Snext; dule</pre>                                  |

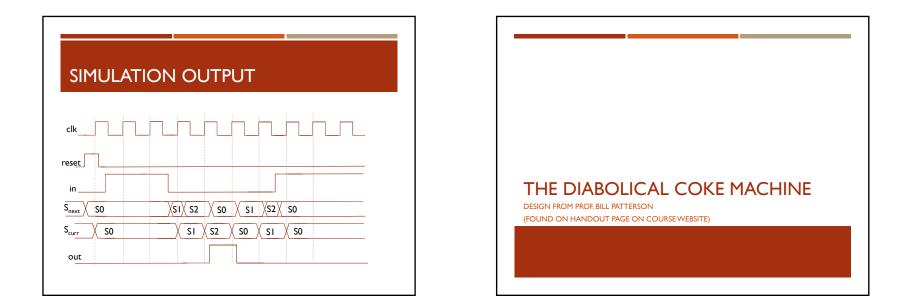

#### MEALY STATE MACHINE EXAMPLE – TESTBECH

```

module example state machine testbench;

wire out;

reg clock, reset, in;

example state machine M0(clock, reset, in, out)

initial

begin

reset = 1'b0;

// initialize inputs

clock = 1'b0;

in = 1'b0;

#4 reset = 1'b1;

#12 \text{ reset} = 1'b0;

#19 in = 1'b1;

#65 in = 1'b0;

#141 in = 1'b1;

#200 $finish;

// end simulation

end

always

begin

#10 clock = ~clock;

end

endmodule

```

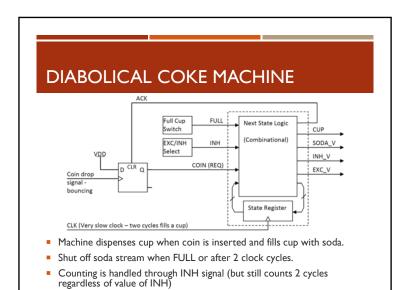

#### STATE TABLE

|       |           |                                |          |          | Style 3 |

|-------|-----------|--------------------------------|----------|----------|---------|

|       | State     |                                | Style 1  | Style 2  | (one-   |

| State | Name      | Function                       | (Binary) | (ad hoc) | hot)    |

| А     | waiting   | Wait for money                 | 000      | 0000     | 000000  |

| В     | release   | Drop a cup                     | 001      | 1000     | 000011  |

| С     | soda_inh1 | Dispense soda with inh 1 cycle | 010      | 0001     | 000101  |

| D     | soda_inh2 | Dispense soda with inh 2 cycle | 011      | 0011     | 001001  |

| E     | soda_exc1 | Dispense soda with exc 1 cycle | 100      | 0101     | 010001  |

| F     | soda_exc2 | Dispense soda with exc 2 cycle | 101      | 0111     | 100001  |

Six state can be encoded in different ways

#### STATE TRANSITION TABLE

| COIN | INH | Pres.<br>State | Q[2:0] | Next<br>State | D[2:0] | со |

|------|-----|----------------|--------|---------------|--------|----|

| 0    | Х   | А              | 000    | А             | 000    | (  |

| 1    | Х   | Α              | 000    | В             | 001    | 1  |

| Х    | 0   | В              | 001    | E             | 100    | >  |

| Х    | 1   | В              | 001    | С             | 010    | )  |

| Х    | 0   | С              | 010    | F             | 101    | )  |

| Х    | 1   | С              | 010    | D             | 011    | )  |

| Х    | 0   | E              | 100    | F             | 101    | )  |

| Х    | 1   | E              | 100    | D             | 011    | )  |

| Х    | Х   | D              | 011    | А             | 000    | )  |

| х    | х   | F              | 101    | Α             | 000    | )  |

| 0] | COIN | INH | Pres.<br>State | Q[3:0] | Next<br>State | D[3:0] |

|----|------|-----|----------------|--------|---------------|--------|

| 0  | 0    | Х   | Α              | 0000   | А             | 0000   |

| 1  | 1    | Х   | Α              | 0000   | В             | 1000   |

| 0  | Х    | 0   | В              | 1000   | E             | 0101   |

| 0  | Х    | 1   | В              | 1000   | С             | 0001   |

| 1  | Х    | 0   | С              | 0001   | F             | 0111   |

| 1  | Х    | 1   | С              | 0001   | D             | 0011   |

| 1  | Х    | 0   | E              | 0101   | F             | 0111   |

| 1  | Х    | 1   | E              | 0101   | D             | 0011   |

| 0  | Х    | Х   | D              | 0011   | А             | 0000   |

| 0  | Х    | Х   | F              | 0111   | А             | 0000   |

State transitions are the same, just different encodings

What about the output signals (CUP, INH\_V, EXC\_V, SODA)?

## OUTPUT TABLE

| Full | Pres. State | Cup | Soda | INH_V | EXC_V |

|------|-------------|-----|------|-------|-------|

| Х    | A           | 0   | 0    | 0     | 0     |

| Х    | В           | I   | 0    | 0     | 0     |

| 0    | C,D         | 0   | I    | I     | 0     |

| I    | C,D         | 0   | 0    | 0     | 0     |

| 0    | E,F         | 0   | I    | 0     | I     |

| I.   | E,F         | 0   | 0    | 0     | 0     |

2 different ways to count

• Logic for these outputs will be different depending on state encoding

#### VERILOG

module coke\_style1 (input full ,inh ,coin ,clk , output reg cup ,inh\_v ,exc\_v ,soda\_v );

reg [2:0] pres\_state, next\_state; // State variables

// State bit assignments

parameter [2:0] waiting = 3'b000, cup\_drop = 3'b001, dispense\_i1 = 3'b010,

dispense\_i2 = 3'b011, dispense\_e1 = 3'b100, dispense\_e2 = 3'b101;

// Next state logic

always @ (pres\_state, coin, inh) begin

case (pres\_state)

waiting: if (coin == 1'b1) next\_state = cup\_drop; else next\_state = waiting;

cup\_drop: if (inh == 1) next\_state = dispense\_i1; else next\_state = dispense\_e1;

dispense\_i1: if (inh == 1) next\_state = dispense\_i2; else next\_state = dispense\_e2;

dispense\_i2: next\_state = waiting;

dispense\_e2: next\_state = waiting;

dispense\_e2: next\_state = waiting;

endcase

end

## VERILOG (CONT.)

// Output logic - note that outputs are reg type even though not ff outputs always @ (pres\_state, full) begin if (pres\_state == cup\_drop) cup = 1; else cup = 0; if (pres\_state == dispense\_i1) | (pres\_state == dispense\_i2) begin inh\_v = ~full; soda\_v = ~full; end if (pres\_state == dispense\_e1 | (pres\_state == dispense\_e2) begin exc v = full; soda\_v = ~full; end end // State register always @ (posedge clk) pres\_state <= next\_state;</pre>

#### endmodule

#### TIMING SIMULATION

- Notice the Coke machine starts filling the cup with soda with inh=1, then switches counting with inh\_v to exc\_v when inh=0.

- The *full* input signal goes high once soda has been dispensed for 2 full cycles.