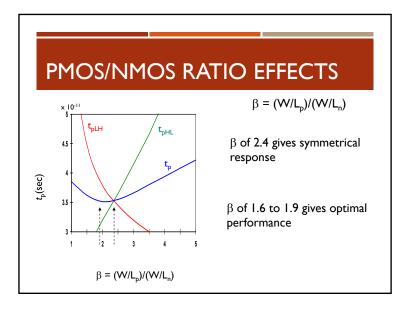

## NMOS/PMOS RATIO

- = So far we have sized the PMOS and NMOS so that the  $R_{eq}$  values match (i.e.,  $\beta = (W/L_p)/(W/L_n) = W_p/W_n = 2 \text{ to } 2.8)$

- Symmetric VTC

- Equal high-to-low and low-to-high propagation delays

- If speed is the only concern, reduce the width of the PMOS device!

- Widening the PMOS degrades the  $t_{pHL}$  due to larger intrinsic capacitance

- What does this imply if we want to minimize delay for an inverter?

## • We define propagation delay as: • $t_p = \frac{t_{pHL} + t_{pLH}}{2} = 0.69C_L \left(\frac{R_{eqn} + R_{eqp} / \beta}{2}\right)$ • And define $C_L = (C_{dp1} + C_{dn1}) + (C_{gp2} + C_{gn2}) + C_W$ $C_L \approx (1 + \beta)(C_{dn1} + C_{gn2}) + C_W$ • So we have

$$t_{p} = 0.345((1+\beta)(C_{dn1} + C_{gn2}) + C_{w})(R_{eqn} + R_{eqp} / \beta)$$

$$t_{p} = 0.345((1+\beta)(C_{dn1} + C_{gn2}) + C_{w})R_{eqn}\left(1 + \frac{r}{\beta}\right), \text{ where } r = \frac{R_{eqp}}{R_{eqn}}$$

• Now, optimize  $t_{p}$  with respect to  $\beta...$

**NMOS/PMOS RATIO**

• Given the equation for

$$t_p$$

:

$t_p = 0.345((1+\beta)(C_{dn1}+C_{gn2})+C_w)R_{eqn}\left(1+\frac{r}{\beta}\right)$

• Minimize  $t_p$  as a function of  $\beta$ ...

• Compute the optimal value of  $\beta$  by setting  $\partial t_p/\partial \beta = 0$

$\beta_{opt} = \sqrt{r\left(1+\frac{C_W}{C_{dn1}+C_{gn2}}\right)}$

Where  $r=R_{eqp}/R_{eqn}=resistance$  ratio for identically sized PMOS, NMOS

$\beta_{opt} = \sqrt{r}$  when  $C_W$  is negligible

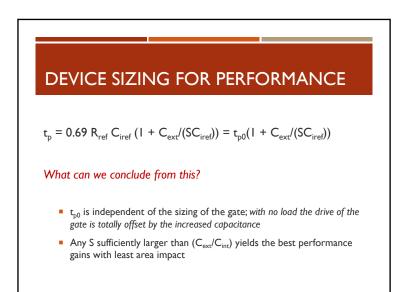

## DEVICE SIZING FOR PERFORMANCE

- Divide capacitive load, C<sub>1</sub>, into

- $C_{int}$ : intrinsic  $\rightarrow$  diffusion

- C<sub>ext</sub>: extrinsic → fanout (gate-channel cap and wiring)

$$t_p = 0.69 R_{eq} C_{int} (I + C_{ext}/C_{int}) = t_{p0} (I + C_{ext}/C_{int})$$

- $t_{p0} = 0.69 R_{eq} C_{int}$  is the intrinsic (unloaded) delay of the gate

- Widening both PMOS and NMOS by a factor S reduces R<sub>eq</sub> by an identical factor (R<sub>eq</sub> = R<sub>ref</sub>/S), but raises the intrinsic capacitance by the same factor (C<sub>int</sub> = SC<sub>iref</sub>)

$t_p = 0.69 R_{ref} C_{iref} (I + C_{ext}/(SC_{iref})) = t_{p0}(I + C_{ext}/(SC_{iref}))$