Sundays 1PM Barus and Holley 190\* bse@brown.edu

## LAB PRINTOUT AND RETURN

- Lab 2 has been graded.

- Jiwon should have sent you an email with comments. Please get back to her with corrections (if needed).

- Lab 9 has been graded (by Prof. Patterson)

- Those who require to resubmit, please redo, print out, and give directly to Prof. Patterson for fast turn around.

- Schematic requirement (for lab 1, 5, 7, 8, or A)

- Print out your schematic and BOM for grading

- This is due by Friday (but please complete sooner, if possible)

### COURSE EVALUATIONS

- Course evaluation forms are now available

- Please access using Banner self service

- Filling out this form provides me with important feedback about your experience with this course.

- Comments are confidential

- Available to me only after grades have been submitted.

- Thanks!

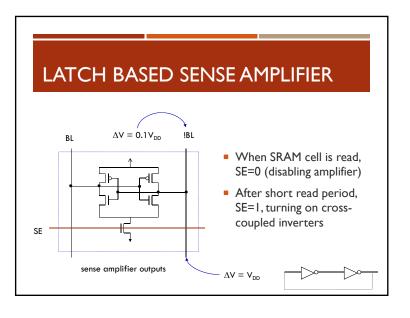

#### **SRAM ARCHITECTURE** Write Enable Din<sub>n-2</sub> Din<sub>1</sub> Din<sub>0</sub> Din<sub>n-1</sub> Column Driver Column Drive Column Driver Column Driver ~ -1 -D A0...An-1 . . . Address -1-Decode ~ ~ $\lfloor - \rfloor$ Sense Amp Sense Amp Sense Amp Sense Amp Dout Dout<sub>n-2</sub> Dout Dout

### 4

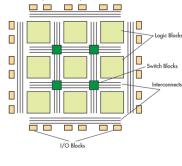

# FIELD PROGRAMMABLE GATE ARRAY (FPGA)

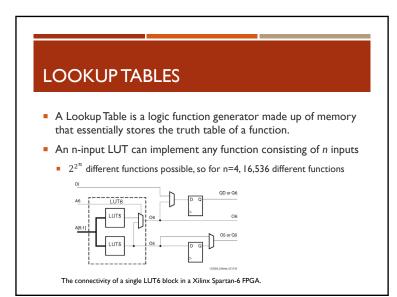

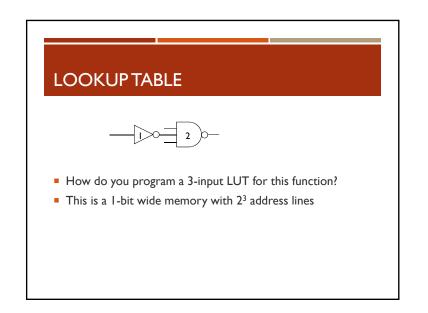

- FPGAs are chips containing configurable logic blocks (CLBs) and programmable interconnect

- Each CLB contains a reprogrammable LookUp Table (LUT) and Flip-Flops for storage.

- The CPLDs you have been using in your labs are scaled back version of FPGAs (10<sup>3</sup> vs. 10<sup>5</sup> logic blocks and less memory)

Symmetrical Array architecture

### MODERN FPGAS

- Modern FPGAs contain many additional specialized blocks:

- Internal memory (Block RAM)

- Memory controllers

- Clock multipliers/dividers

- Digital signal processing (DSP) units for fast arithmetic

- Bus interfaces

- Simple processors (e.g., ARM)

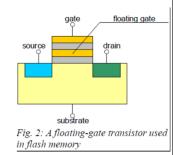

### LUT MEMORY CELLS

It is convenient to program the FPGA and then retain that programming even when disconnected from power (i.e., using non-volatile memory.

• One way to do this is with

flash-memory based FPGAs

### FLOATING GATE TRANSISTOR

- Gate is electrically isolated, creating a floating node.

- A number of inputs are deposited above the floating gate and are electrically isolated from it.

- Since the floating gate is completely surrounded by a highly resistive material, the charge remains unchanged.

6