# DIGITAL ELECTRONICS SYSTEM DESIGN

**FALL 2019**

**PROF. IRIS BAHAR**

OCTOBER 7, 2019

LECTURE 10: CMOS TRANSIENT BEHAVIOR

#### **SCHEDULE THIS WEEK**

- Jiwon Choe will be covering my lecture this Wednesday

- Introduction to sequential logic

- McKenna Cisler will be holding a Verilog tutorial this THURSDAY from 5-7pm in the fishbowl

- He will be swapping his usual Wednesday hours with Andrew

# **NMOS I-V SUMMARY**

Shockley I<sup>st</sup> order transistor models

$$I_{ds} = \begin{cases} 0 & V_{gs} < V_{th} & \text{cutoff} \\ \beta \left( V_{gs} - V_{th} - \frac{V_{ds}}{2} \right) V_{ds} & V_{gs} < V_{dsat} & \text{linear} \\ \frac{\beta}{2} \left( V_{gs} - V_{th} \right)^2 & V_{ds} > V_{dsat} & \text{saturation} \end{cases}$$

$$eta = \mu C_{ox} rac{W}{I}$$

where  $\mathsf{C}_{o\mathsf{x}}$  is the capacitance per unit area of  $\mathsf{SiO}_2$

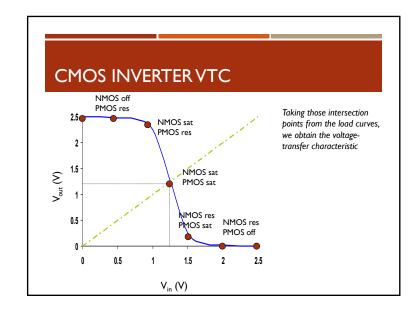

#### SWITCHING THRESHOLD

- Define  $V_M$  to be the point where  $V_{in} = V_{out}$  (both PMOS and NMOS in saturation since  $V_{DS} = V_{GS}$

- If  $V_M = V_{DD}/2$ , then this implies symmetric rise/fall behavior for the CMOS gate

- Recall at saturation,  $I_D = (k'/2)(W/L) (V_{GS} V_{th})^2$ ,

- where  $k'_n = \mu_n C_{ox} = \mu_n \varepsilon_{ox} / t_{ox}$

- Setting  $I_{Dp} = -I_{Dn}$   $\frac{k'_n}{2} \frac{W_n}{L_n} (V_M V_{thn})^2 = \frac{k'_p}{2} \frac{W_p}{L_n} (V_M V_{thp})^2$

- Assuming  $V_{thn}=-V_{thp}$   $\frac{W_p}{V_n}/L_p = \frac{k_n'}{k_p'} = \frac{\mu_n}{\mu_p}$ , if  $L_p=L_n$ ,  $W_p=W_n\cdot\frac{\mu_n}{\mu_p}$

## MOS STRUCTURE RESISTANCE

The simplest model assumes the transistor is a switch with an infinite "off" resistance and a finite "on" resistance Ron

$$V_{GS} \geq V_T$$

$$S \circ \underbrace{\hspace{1cm}}_{R_{on}} R_{on} \circ D$$

- However R<sub>on</sub> is nonlinear, time-varying, and dependent on the operation point of the transistor

- How can we determine an equivalent (constant and linear) resistance to use instead?

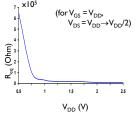

## MOS STRUCTURE RESISTANCE

- Approximate  $R_{on}$  as the resistance found during linear operation

- Simple to calculate but limited accuracy

- Instead use the average value of the resistances, R<sub>eq</sub>, at the end-points of the transition (i.e.,  $V_{DD}$  and  $V_{DD}/2$ )

0.5

1.5

# **EQUIVALENT MOS STRUCTURE RESISTANCE**

$$R_{eq} = \frac{3}{4} \frac{V_{DD}}{I_{DQ, qp}}$$

$$I_{DSAT} = \frac{\mu C_{ox}}{2} \frac{W}{L} \left( (V_{DD} - V_T) V_{DSAT} - \frac{V_{DSAT}^2}{2} \right)$$

$$R_{eq} = \frac{3}{2\mu C_{ax}} \frac{L}{W} \frac{V_{DD}}{(V_{DD} - V_T)V_{DSAT} - \frac{V_{DSAT}^2}{2}}$$

$$R_{eq_{NMOS}} \propto \frac{L}{\mu_n W},$$

$R_{ed}$  is essentially independent of  $V_{DD}$  as long as  $V_{DD} >> V_T + V_{DSAT}/2$

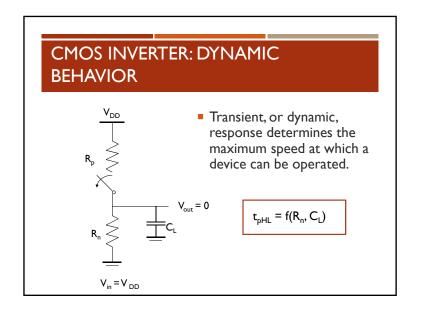

#### **INVERTER PROPAGATION DELAY**

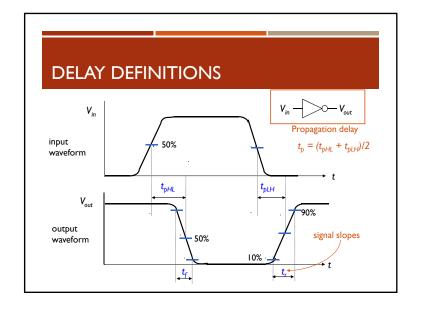

Propagation delay proportional to time-constant of network formed by ON resistor and the load capacitance.

$$t_{pHL} = f(R_n, C_L)$$

$$R_n = R_{eq} = \frac{3}{4} \frac{V_{DD}}{I_{DSAT}}$$

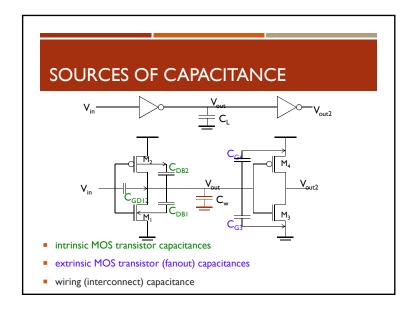

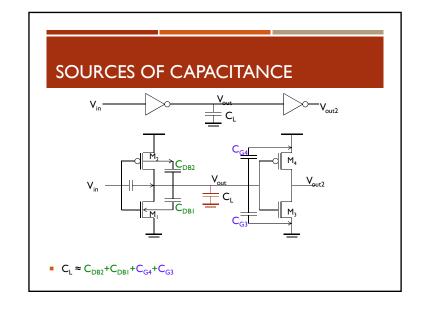

$$C_L = C_{int} + C_{ext}$$

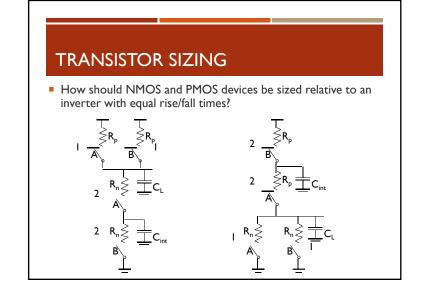

Want to have equal rise/fall delays make R<sub>n</sub>=R<sub>o</sub>

# MODELING PROPAGATION DELAY

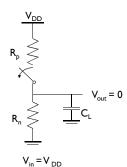

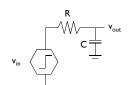

■ Model circuit as first-order RC network

$$v_{out}(t) = (I - e^{-t/\tau})V_{in}$$

where

$$\tau = RC$$

Time to reach 50% point is  $t = ln(2) \tau = 0.69 \tau$

Time to reach 90% point is  $t = ln(9) \tau = 2.2 \tau$

$$t_p = (t_{pHL} + t_{pLH})/2 = 0.69C_L(R_n + R_p)/2$$

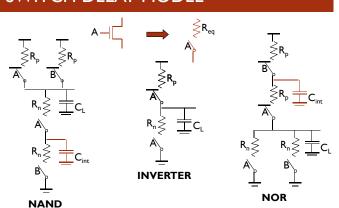

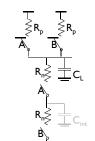

# **SWITCH DELAY MODEL**

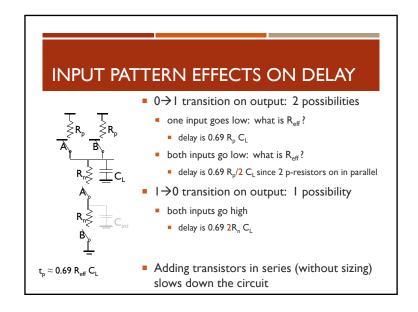

# INPUT PATTERN EFFECTS ON DELAY

- Delay is dependent on the pattern of

- Ist order approximation of delay:

$$t_p^{}\approx 0.69~R_{eff}^{}~C_L^{}$$

R<sub>eff</sub> depends on the input pattern