## Verilog modules

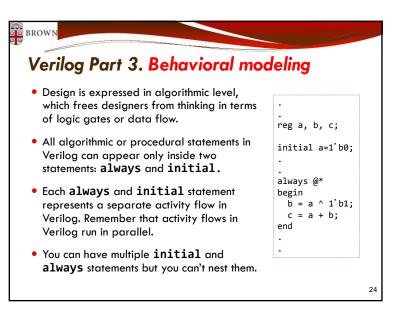

- The functionality of each module can be defined with 3 modeling levels:

- Structural (or gate level)

- Dataflow level

- Behavioral (or algorithmic level)

- Verilog allows different levels of abstraction to be mixed in the same module.

# Modules and ports

```

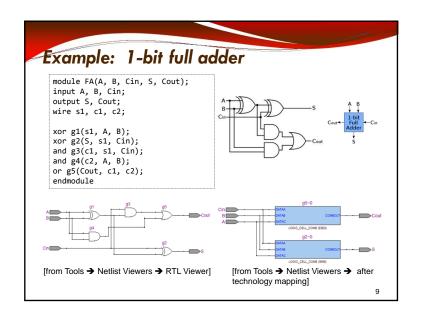

module FA(A, B, Cin, S, Cout);

input A, B, Cin;

output S, Cout;

...

endmodule

```

- All port declarations (input, output, inout) are implicitly declared as wire.

- If an input should hold its value, it must be declared as reg.

```

module FA(input A, input B, input Cin, output S, output Cout); \dots endmodule

```

6

# Verilog Part 1. Structural modeling

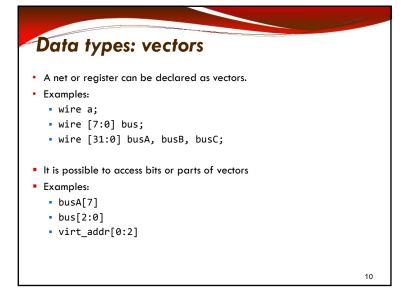

- Data types: bits

- Nets represent connections between hardware elements.

- of connected devices.

Nets are declared using the

· Continuously driven by the output

Nets are declared using the keyword wire.

- wire c1, c2;

- wire d=0;

7

# Gate level modeling

```

wire Z, Z1, OUT, OUT1, OUT2, IN1, IN2;

and a1(OUT1, IN1, IN2);

nand na1(OUT2, IN1, IN2);

xor x1(OUT, OUT1, OUT2);

not (Z, OUT);

buf final (Z1, Z);

```

- Describes the topology of a circuit

- All instances are executed concurrently just as in hardware

- Instance name is not necessary

- The first terminal in the list is an output; others are inputs

- Not the most interesting modeling technique for this class

```

wire [7:0] OUT, IN1, IN2;

// array of gates instantiations

nand n_gate [7:0] (OUT, IN1, IN2);

// which is equivalent to the following

nand n_gate0 (OUT[0], IN1[0], IN2[0]);

nand n_gate1 (OUT[1], IN1[1], IN2[1]);

nand n_gate2 (OUT[2], IN1[2], IN2[2]);

nand n_gate3 (OUT[3], IN1[3], IN2[3]);

nand n_gate4 (OUT[4], IN1[4], IN2[4]);

nand n_gate5 (OUT[5], IN1[5], IN2[5]);

nand n_gate6 (OUT[6], IN1[6], IN2[6]);

nand n_gate7 (OUT[7], IN1[7], IN2[7]);

```

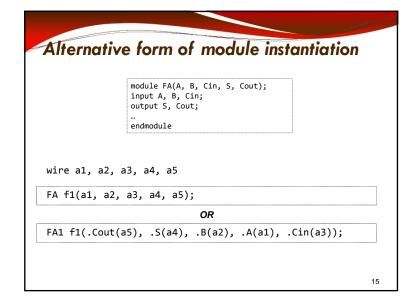

```

Module instantiation

module fulladd4(A, B, Cin, S, Cout);

input [3:0] A, B;

input Cin;

output [3:0] S;

output Cout;

wire C1, C2, C3;

FA f1(A[0], B[0], Cin, S[0], C1);

FA f2(A[1], B[1], C1, S[1], C2);

FA f3(A[2], B[2], C2, S[2], C3);

FA f4(A[3], B[3], C3, S[3], Cout);

endmodule

FALT2

FALT2

FALT2

FALT3

FALT4

FALT5

FALT5

```

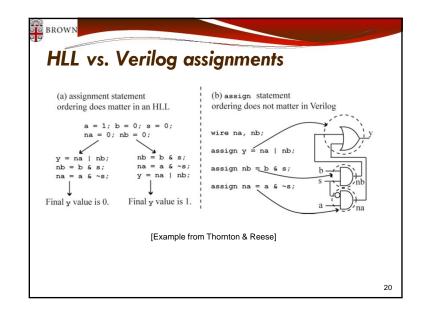

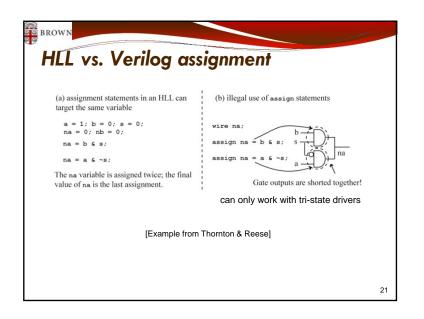

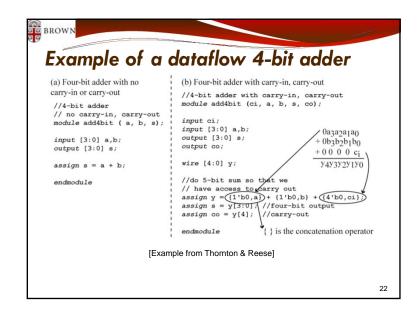

# Verilog Part 2. Dataflow modeling

- Module designed by specifying data flow: Designer is aware of how data flows between registers and how it is processed in the design

- The continuous assignment is one of the main constructs used in dataflow modeling

- assign out = i1 & i2;

- assign addr[15:0] = addr1[15:0] ^ addr2[15:0];

- assign {c\_out, sum[3:0]}=a[3:0]+b[3:0]+c\_in;

- A continuous assignment is always active and evaluated as soon as one of its right-hand-side variables change

- Assign statements describe hardware that operates concurrently

Ordering does not matter

- Left-hand side must be scalar or vector net. Right-hand side operands can be wires, (registers, integers, and real)

# Examples: 2x1 MUX and 4x1 MUX

```

module mux2to1(s, a, b, y);

output y;

input s, a, b;

assign y = (b & s) | (a & ~s);

// OR THIS WAY

assign y = s ? b : a;

endmodule

```

19

# Operator types in dataflow expressions

- Operators are similar to C except that there are no ++ or conventions allowed.

- Arithmetic: \*, /, +, -, % and \*\*

- Logical: !, && and | |

- <u>Relational:</u> >, <, >= and <=

- Equality: ==, !=, === and !==

- Bitwise:  $\sim$ , &,  $\mid$ ,  $^{\wedge}$  and  $^{\wedge}\sim$

- <u>Reduction:</u> &, ~&, |, ~|, ^ and ^~

- Shift: << and >>

- Concatenation: { }

- Replication: {{}}

- Conditional: ?:

#### Data types: reg, parameter

- reg: Verilog variable type (does not necessarily imply a physical register). Think of it as a variable or place holder. Unsigned by default

- reg clock;

- reg[0:40] virt\_addr;

- Register arrays or memories: Used to model register files, RAMs, ROMs. Modeled in Verilog as a 1-dimensional array of registers.

- reg mem1bit[0:1023];

- reg[7:0] membyte[0:1023];

- To access an element in an memory array: membyte[511];

- parameters: Define constants and cannot be used as variables.

- parameter port\_id=5;

25

#### initial statements • An initial block start at time 0, executes exactly once and then never again. • If there are multiple initial blocks, each blocks starts to execute concurrently at time 0 and each blocks finish execution independently of the others. • Multiple behavioral statements must be grouped using **begin** and end. If there is one statement then grouping is not necessary. reg x, y, m; In procedural statements (initial, initial m=1'b0; always) LHS must be of type registers initial (and its derivatives) begin x = 1'b0;y = 1'b1;end 27

### Data types

• Integers: (signed and real): They are of type reg.

```

real delta;

integer i;

initial

begin

delta = 4e10;

i=4;

end

```

Arrays of integers and reals:

```

integer count[0:7];

Integer matrix[4:0][0:255];

```

Strings: can be stored in reg. The width of the register variables must be large enough to hold the string.

```

reg [8*19:1] string_value;

initial

string_value = "Hello Verilog World";

```

26

## BROWN

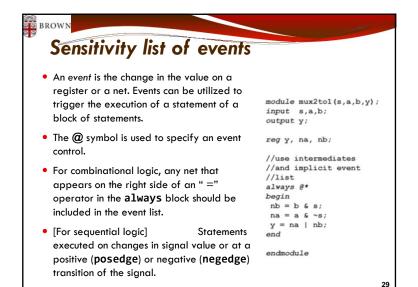

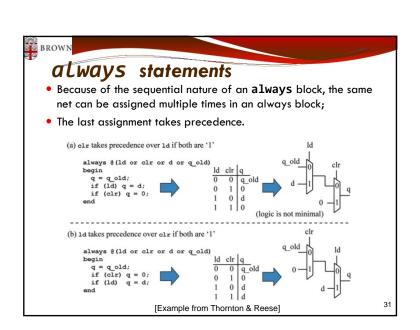

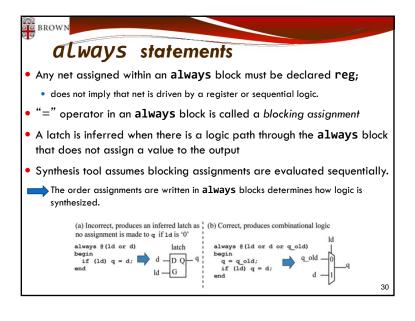

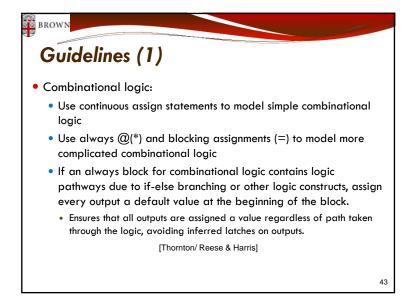

# always statements

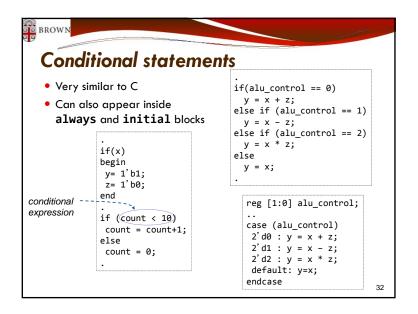

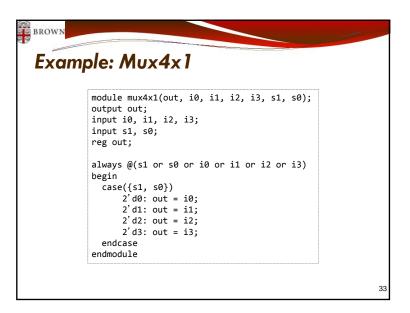

- The always statement starts at time 0 and executes the statements in the always block when the events in its sensitivity list occur

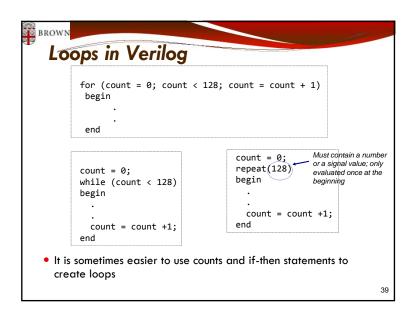

- Powerful constructs like if, if-else, case, and looping are only allowed inside always blocks.

- always statements can be used to implement both combinational or sequential logic

- Multiple behavioral statements must be grouped using begin and end.

- Multiple always statement can appear in a module

module mux2to1(s,a,b,y);

input s,a,b;

output y;

reg y;

//use boolean ops

always @(a or b or s)

begin

y = (b & s) | (a & ~s);

end

endmodule

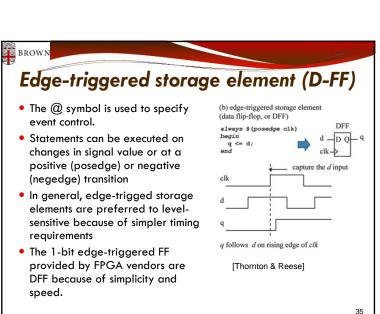

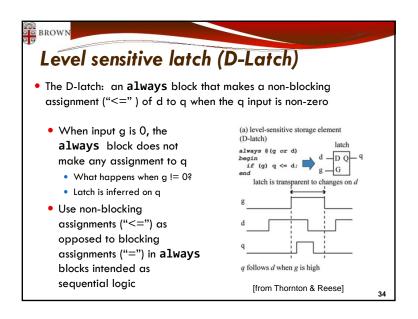

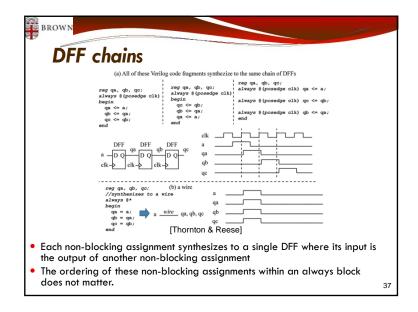

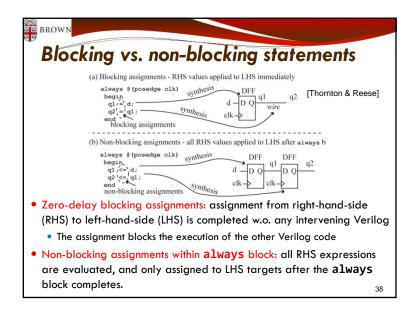

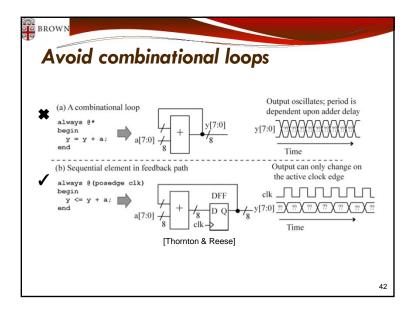

# Sequential logic: Use non-blocking assignments (<=) in always blocks that are meant to represent sequential logic Use posedge sensitivity to ensure DFF Do not make assignments to the same signal in more than one always statement or continuous assign statement Avoid mixing blocking and non-blocking assignments in the same always block. [Thornton/ Reese & Harris]

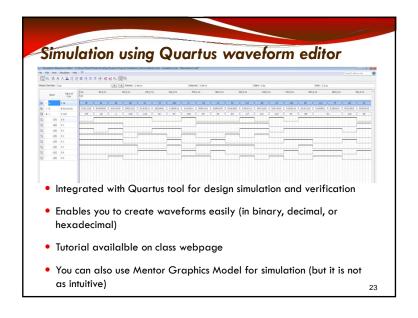

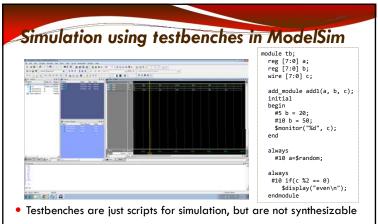

- New Verilog commands enable precise timing simulation and monitoring of outputs.

- Need to learn to work with it for Mentor Graphics ModelSim

- Optional for this class

45